@饭统戴老板:关于 7nm 和 9000s 的良率,写一点儿能写的东西。

1. 先从台积电的 7nm 工艺开始说起。2017 年台积电开始试产 7nm,由于期间经历了光刻机从 DUV 到 EUV 的升级,所以 7nm 制造本身又被分成三代:第一代 7nm 工艺叫 N7、第二代 叫做 N7P,第三代叫做 N7+;

2. 台积电前两代用的是 DUV 光刻机,第三代用的是 EUV 光刻机。而三星 7nm 搞的晚,一开始就用上了 EUV。EUV 带来了更好的成本和良率,DUV 工序更复杂但也能搞定,所以 7nm 就成了唯一既能用 DUV 做,也能用 EUV 做的一代工艺。

3. 用 DUV 怎么来做 7nm 芯片?台积电内部也经历了多次工艺迭代(可以参考知乎上的一篇文章 [1],这里不赘述),最终使用了 DUV+SAQP(自对齐四重曝光)工艺把良率从 70% 磨到了 90% 以上 —— 这是一个相当重要的数字。

4. 另外需要知道的是:DUV 光刻机的几代型号,1980Di、2000i 和 2050i,都可以支撑 SAQP 工艺下的 7nm。后两者现在进不来,但 1980Di 目前没问题,国内也有很多存量设备。

6. 能讲的大概也就这些了。说一个现在很多人关心的问题:7nm 的良率能到多少?

7. 9000s 刚出来那会儿,海外有很多人宣称良率只有 10%,国内也有不少人起哄。而从台积电之前的历史来看,DUV+SAQP 虽然肯定比 EUV 路线的成本高,但本身良率是可以做到 90% 以上的。

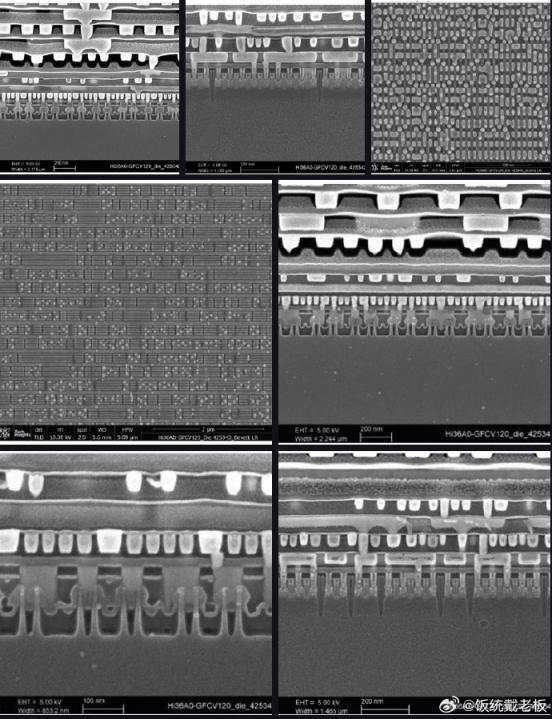

8. 海外媒体 TechInsights 在 9 月份做了拆解,发现晶体管的沟道、栅极和漏极以及触点和下部金属层看起来相当干净,这在低产量的工艺下是做不到的,因此良率应该是要远高于此前大众认知的 10%。

10. 另一家智库 SemiAnalysis 的信源指出,9000s 的缺陷密度(D0)为 0.14,虽然只有台积电 N5 工艺的一半,但已逼近三星成熟的 7nm 工艺。SemiAnalysis 的原话是 [2]:“一些专家所说的 10% 的良率数字是无稽之谈。”

11. 上述都是反驳 “10% 良率论”,那有没有大佬直接对 9000s 的良率下一个判断呢?有,就是台积电高管的林本坚,“浸润式之父”,跟梁梦松当年并称 “研发六骑士”,他 9 月份在哈佛的一场座谈会上下了判断:良率大概 50%。

12. 综合,可以下一个大概结论:目前良率 50%+,并且不断攀升,最终可以做到 90%+。7nm+90% 的良率,会对国内芯片产业 —— 尤其是日益紧缺的 AI 算力领域 —— 产生深远的影响,而这种影响才刚刚开始。

13. DUV 可不可以做 5nm 呢,也就是 N+3 工艺?理论上可以,但没人做过,SemiAnalysis 估计用 DUV 做 5nm 要比用 EUV 的成本高 55~60%。要是真的是这样一个数字,整个张江晚上都不要睡了,因为只要一睡就会笑醒。

14. 看过我之前拆的 H100 的成本结构(台积电 5nm + 工艺)就知道,台积电的制造成本只占 H100 售价的 5% 不到,麒麟和升腾定价没有 H100 那么霸气十足,但制造成本的上升也完全能够消化 —— 只要能造出来,就完全不愁卖。

15. 那到底能不能搞出来?不知道,反正放低预期,不要沸腾,慢慢等待就好。最坏的时刻过去了吗?也没有,未来还会有很多严峻的考验,有突破的时候少沸腾一些,煎熬的时候才会少一些冷嘲热讽。

16. 上海 IC 基金连续投了张江某厂两轮,是第三大股东,17 年底我离开的时候,项目还在打桩搞基建。如果未来一个 “现在可以说了” 的系列,我应该是最适合执笔的,希望我这个号能熬到可以写的那一天吧。